机构名称:

¥ 2.0

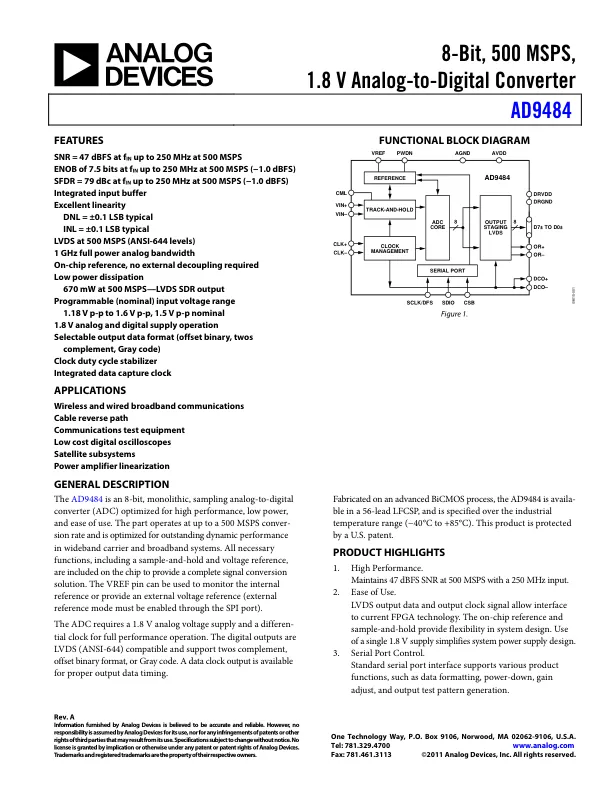

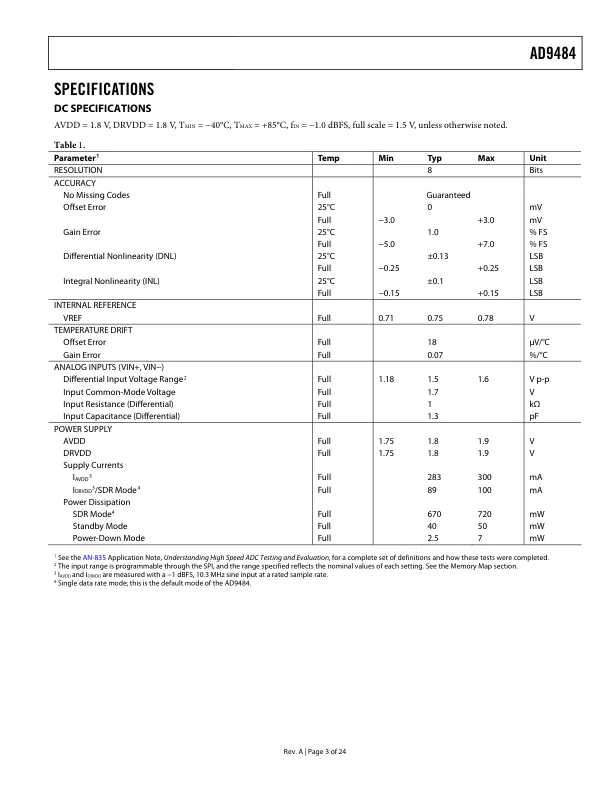

SNR = 47 dBFS,f IN 高达 250 MHz,500 MSPS ENOB 为 7.5 位,f IN 高达 250 MHz,500 MSPS(−1.0 dBFS) SFDR = 79 dBc,f IN 高达 250 MHz,500 MSPS(−1.0 dBFS) 集成输入缓冲器 出色的线性度 DNL = ±0.1 LSB 典型值 INL = ±0.1 LSB 典型值 LVDS,500 MSPS(ANSI-644 级别) 1 GHz 全功率模拟带宽 片上基准电压源,无需外部去耦 低功耗 670 mW,500 MSPS—LVDS SDR 输出 可编程(标称值)输入电压范围 1.18 V p-p 至 1.6 V p-p,1.5 V p-p 标称值 1.8 V 模拟和数字电源操作 可选输出数据格式(偏移二进制、二进制补码、格雷码) 时钟占空比稳定器 集成数据采集时钟

AD9484 | 8 位、500 MSPS、1.8 V 模数转换器